Read-Write Analyzers 1632 – Obsolete

320 Mbit/s PRML Channel Analyzer

160 Mbit/s Peak Detector Channel Analyzer

- PR4, EPR4, E2PR4 Modes up to 320 Mbits/s

- Peak Detector Mode up to 160 Mbits/s

- Programmable Clock Recovery

- 320 Mflux/s Pattern Generator

- 12 Tap 12 Bit Equalizer (60 to 200 Mbits/s)

- 24 Tap 12 Bit Equalizer (80 to 320 Mbits/s)

- Optional PRML Channel Chips Integration

- Optional 2 Gsample/s ADC

New PRML Tests:

- Margin-Type Prediction of Error Rate

- Sample Value Distribution

- Non-linear Transition Shift (NLTS)

The GUZIK RWA-1632 Read/Write Analyzer provides comprehensive PRML (Partial Response Maximum Likelihood) and Peak Detector channel evaluation facilities. PRML channel testing is based on an advanced, proprietary, clock recovery system. Digitized analog signals are stored in memory and analyzed by a high speed multi-channel DSP.

In addition to the standard tests performed with the Peak Detector channels, several new tests have been added in order to evaluate and optimize the PRML channel. These tests include programmable and adaptive equalization with an Analog Equalizer, NLTS measurements, histograms of Sample Distribution Values to control the quality of Partial Response (PR) channel, direct measurement of Bit Error Rate, estimation of Error Rate, adaptive Precompensation, etc.

The RWA-1632 supports all established methods of NLTS measurement: spectral elimination (5th harmonic), pseudo-random sequence autocorrelation, and comparing linear superposition of pulses with a measured dibit.

Also, the RWA-1632 provides a margin-type estimation of error rate from the output of the PRML channel (SAM, Error Filters, Partial Histograms). Error rate estimations, with correlated and uncorrelated noise, are based on predictive performance of maximum likelihood detectors.

Different PRML channel chips can be integrated for testing using the replaceable plug-in Chip Adapter module.

The WITE (Windows Integrated Test Environment) software package allows the user to capture Sampled Value Distributions and Eye diagrams generated from the sampled data, along with all the standard Peak Detector and PRML channel tests.

Features:

320 Mbit/s data rate for PRML channel.

160 Mbit/s data rate for Peak Detector channel.

Programmable Clock Recovery.

Optional PRML chip integration by plug-in module.

12 tap 12 Bit Analog Equalizer.

Optional 24 tap 12 Bit Analog Equalizer.

Histogram of sample distributions.

Eye Diagram Plot.

Direct Bit Error Rate Measurement.

Non-Linear Transition Shift Measurements

- 5th Harmonic Measurement.

- Pseudo-Random pattern autocorrelation .

- Pulse Shape Best Fit.

Comparator error rate with Viterbi algorithm implemented in DSP.

Error Rate Estimation.

Digital scope mode.

Direct Access to Sampled Data in Memory.

Programmable Pattern Generator with random pattern length up to 32 Kbytes and hierarchical pattern structure.

Programmable write data Precompensation of individual bits with 20 ps resolution.

Analog Channel 961:

- Bandwidth: 0.1 to at least 250 MHz at -3 dB

- Flatness: 0.1 to 100 MHz at ± 0.2 dB

- Programmable Attenuator: 36 dB in 2 dB steps

- Filters: 3 low pass (custom cutoff frequencies up to 160 MHz);

8 overwrite from .5 to 20 Mhz;

high/band pass filters available for measuring Popcorn

- Write Current: Programmable 0 to 80mA in 0.02mA steps

- MR Read Bias: Programmable -20 to 20mA in 0.01mA steps

- Differentiators: Two plug-in positions for custom modules up to 160 Mflux/s. 5 modules shipped standard for data ranges from 5 to 160 Mflux/s

12 Tap Equalizer:

- Bandwidth: 0.1 to at least 130 MHz at -3 dB

- Flatness: 0.1 to 90 MHz at ± 0.2 dB

- Control: 12 tap 12 bit resolution

24 Tap Equalizer:

- Bandwidth: 0.1 to at least 160 MHz at -3 dB

- Flatness: 0.1 to 100 MHz at ± 0.2 dB

- Control: 24 tap 12 bit resolution

Clock Recovery:

- PR4, EPR4, E2PR4 modes.

- Variable target support.

- Programmable loop bandwidth to .5 MHz

- Jitter: 20 ps RMS (200 MHz)

1632 Write Channel:

- Frequency Synthesizer: Up to 1GHz with 0.01% resolution

- Pattern Generator: Data rates to 320 Mflux/s. Any user specified data pattern up to a maximum of 32 Kbytes of encoded data and hierarchical pattern structure.

- Precompensation: Individual Bit Precompensation with resolution 20 ps

- Jitter: 3ps RMS

Data Rate:

- PRML: 320 Mbits/s.

- Error Rate Analyzer: Up to 240 Mbits/s, limited by channel chip used.

- Peak Detector: 5 to 160 Mflux/s.

Bit Shift Analyzer:

- Accuracy: better than 100 ps

- Repeatability: better than 50 ps

- Resolution: 20 ps

- Jitter: 40 ps RMS

- Window Centering: 100 ps

Digital Pulse Profile Mode:

- Single shot mode 200 Msamples/s, 2 Gsamples/s with optional ADC. 8 bit ADC.

- 250 MHz analog bandwidth.

- Up to 20 ps resolution.

Parametric Measurement Accuracy:

- TAA: ± 1.5%

- Modulation: ± 2.0%

- SNR: ± 0.5 dB

- Crest factor: ± 2.0%

- Overwrite: ± 0.3 dB

- Pulse width: ± 2.0%(without Digital Pulse profile).

Options:

- High-speed Digitizer 2 Gsample/s.

- High-speed Pattern Generator 320 Mflux/s.

- 24 Tap 12 Bit Analog Equalizer.

- Plug-in PRML Chip module.

Currently available modules:

SSI 4901

SSI 4910

SSI 4915Additional PRML chips may be integrated upon request.

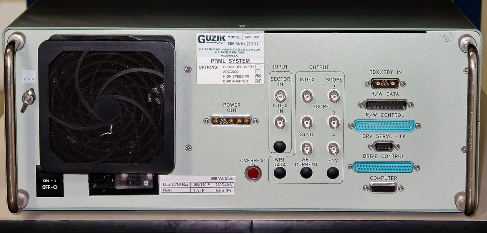

Physical Parameters:

RWA-1632

Size 21.6″ x 17.6″ x 7.3″ Weight 30 lb. Power 100/120 vac ± 10%, 50/60 Hz, 4.0 amps approximately

220/240 vac ± 10%, 50/60 Hz, 2.0 amps approximately

Universal Input

ANALOG CHANNEL 961

Size 19.0″ x 17.6″ x 3.3″ Weight 10 lb. Power Supplied from RWA-1632